尋夢新聞LINE@每日推播熱門推薦文章,趣聞不漏接❤️

集微網消息,物聯網的萬億級別市場正在逐步形成,超萬億級的設備和節點將通過物聯網技術實現萬物互聯和萬物智聯。但是受限於體積、重量和成本等因素,物聯網節點需要在微型電池或能量收集技術進行供電的情況下,能夠持續工作數年乃至十年以上,這對晶片提出了苛刻的低功耗要求。

在低功耗、電池供電的物聯網設備正處於爆發性增長態勢的背景下,如何才能真正滿足物聯網設備的低功耗、低成本需求呢?為此,2020年5月27日(周三)上午10:00,集微網邀請芯原微電子(上海)股份有限公司副總裁汪洋做客第九期「開講」,帶來以《超低功耗物聯網連接方案與先進半導體工藝技術的結合》為主題的精彩演講。截至5月28日中午12:00,已有11488名觀眾通過愛集微APP直播平臺觀看了該節目。

點擊此處觀看回放

芯原微電子(上海)股份有限公司副總裁汪洋

適用於物聯網市場FD-SOI 22nm工藝

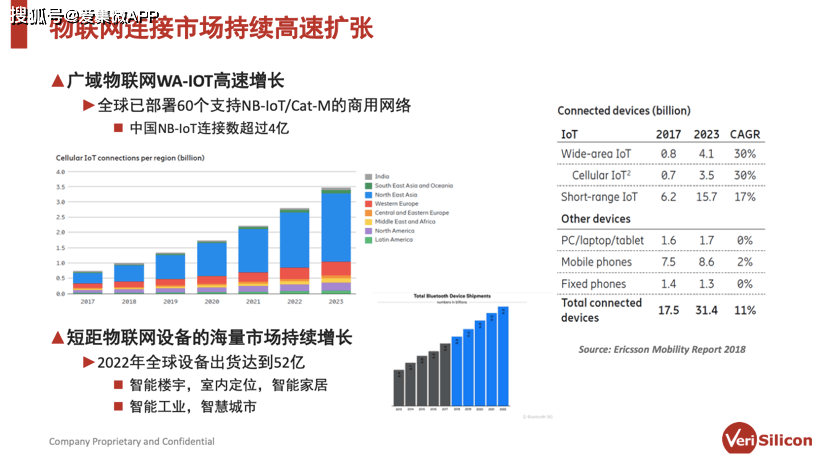

在汪洋看來,如今的物聯網連接市場正持續高速擴張。物聯網主要分為廣域物聯網和短距物聯網,其中廣域物聯網主要包括NB-IoT和Cat-M,目前全球已部署60個支持NB-IoT/Cat-M的商用網路;而短距物聯網包括WiFi、藍牙BLE和LoRa等等,主要應用於智能樓宇、室內定位、智能家居、智能工業、智慧城市等海量市場,該市場正呈現持續增長趨勢,預計2022年全球設備出貨達到52億。

展開全文

「對於芯原而言,將主要選擇以NB-IoT和藍牙BLE為代表的IoT連接技術,並會根據5G場景下的不同應用進行持續演進。」汪洋說道。

實際上不管是廣域物聯網,還是短距物聯網,對於IoT設備系統平臺的需求都是相似的。其中基於IP的硬件平臺,可以結合工藝的特點來滿足其完整性和可靠性,而面向應用場景的軟體平臺則需要滿足可擴展和場景化的需求。

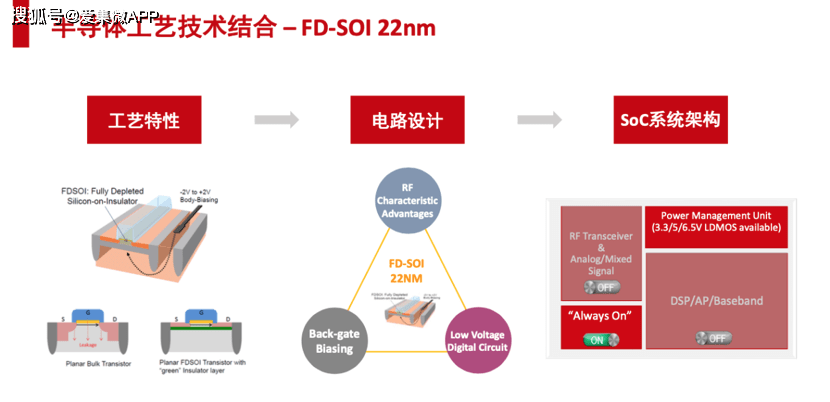

汪洋指出,基於IP的硬件平臺需要與半導體工藝技術結合。「隨著半導體工藝技術節點不斷向前演進,對漏電控制的要求會越來越高,經過芯原的比較和選擇,認為FD-SOI 22奈米是最合適的工藝技術。」

為什麼FD-SOI工藝適用於物聯網市場呢?這主要歸功於它的三個特點:一是低功耗,FD-SOI獨有的體偏壓(body bias)可通過用軟體控制體偏壓在功耗、性能和漏電功耗之間實現動態平衡;二是FD-SOI更容易集成RF工藝,FD-SOI可以為射頻設計提供超優的RF特性,可以支持更高的射頻頻段,包括毫米波頻段,射頻電路匹配性能更好;三是FD-SOI能夠支持物聯網超低電壓晶片的實現。

汪洋表示,「將採用FD-SOI 22奈米工藝的芯原IP集成到SoC中,可以滿足物聯網設備對於低成本、低功耗、高集成度的三個需求。」

經過芯原的多方面測試,FD-SOI 22奈米工藝的射頻優勢主要體現在5個方面:一是高電流效率Gm/I,支撐低噪聲高增益的射頻電路設計;二是更優的器件匹配度可幫助減少電路面積;三是更低的漏/源極寄生效應;四是通過back-gate biasing可靈活調整MOS管閾值電壓,支持更多射頻電路新結構;五是通過控制back-gate 電壓可簡化實現射頻電路校準和微調。

芯原的多種IP產品

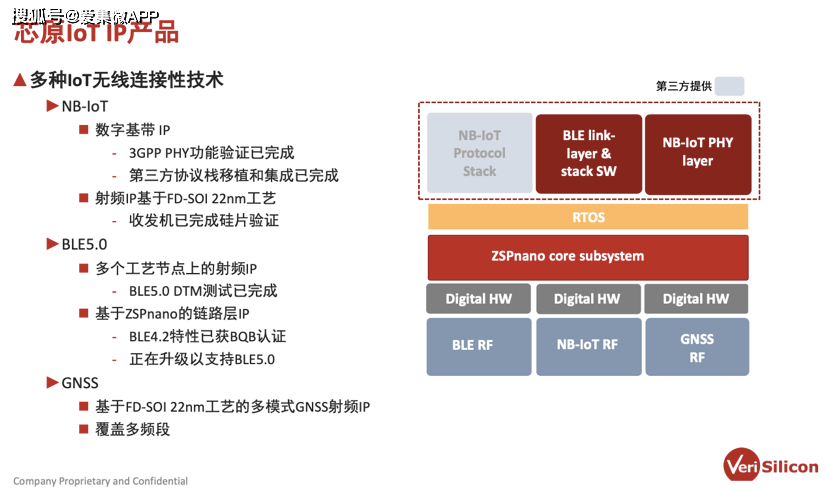

從芯原的布局來看,其擁有多種IoT無線連接性技術,IP產品主要包括NB-IoT數字基帶IP和射頻IP、藍牙BLE5.0射頻IP和基於ZSPnano的鏈路層IP、多模式GNSS射頻IP。

芯原NB-IoT IP

據汪洋介紹,在NB-IoT技術方面,芯原可以提供包括RF、收發器、基帶、處理器和電源管理組件的高效單晶片集成。

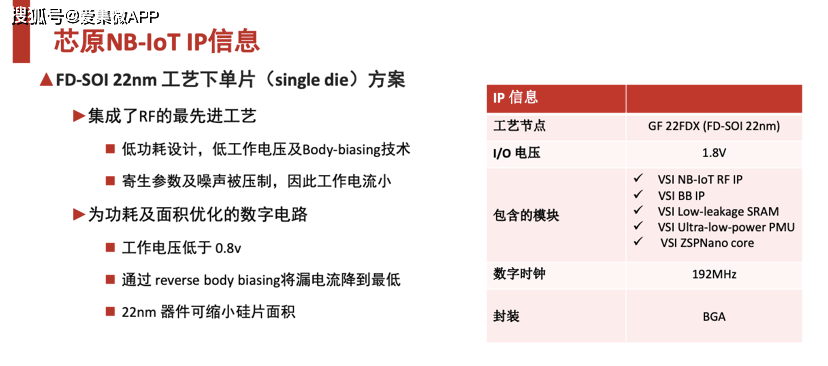

芯原NB-IoT IP是FD-SOI 22奈米工藝下的單片方案,其集成了RF的最先進工藝,不僅採用低功耗設計,低工作電壓及Body-biasing技術,同時由於寄生參數及噪聲被壓制,因此工作電流很小;此外其擁有為功耗及面積優化的數字電路,不僅工作電壓低於0.8v,同時通過reverse body biasing將漏電流降到最低,22nm器件可縮小矽片面積。

值得一提的是,基於FD-SOI 22奈米工藝上的芯原NB-IoT射頻IP是一個完整收發機,其擁有的幾大亮點包括:無電感高增益 LNA、低 IF/zero IF 可配置 RX 架構、用於校準的TRX loopback、支持26MHz DCXO/VCTCXO和集成PMU。

而芯原NB-IoT 數字基帶處理IP是基於ZSPnano core的單核基帶處理,ZSPnano集MCU和DSP功能及特性於一身,其擁有低功耗、低成本的內核架構,以及全系統集成和驗證。

從芯原NB-IoT 基帶測試報告來看,在標準符合性測試方面,不僅使用第三方協議棧軟體通過了PHY功能的系統測試,同時通過了R&S CMW500 測試儀的信令測試;此外在功耗測試方面,不僅內核電壓可低至 0.65v,同時通過body-biasing技術將漏電流降至了最低。

芯原藍牙BLE IP

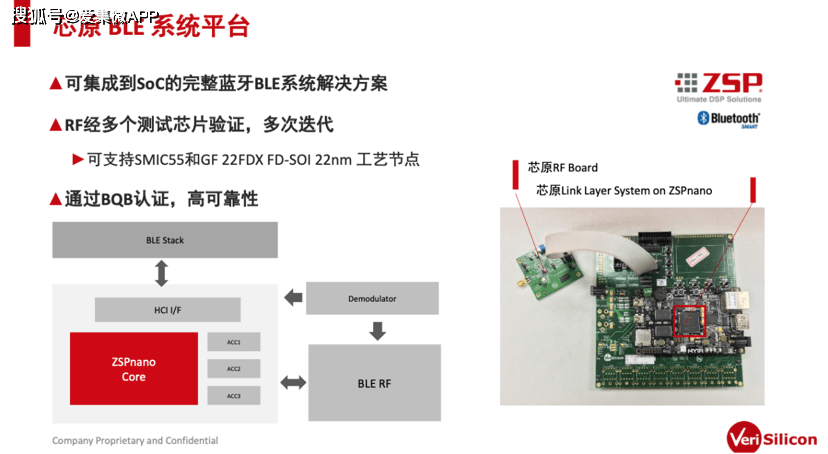

據汪洋介紹,在藍牙BLE技術方面,芯原BLE系統平臺是可集成到SoC的完整藍牙BLE系統解決方案。芯原BLE RF經多個測試晶片驗證,多次迭代,可支持SMIC55和GF 22FDX FD-SOI 22nm工藝節點。此外,芯原BLE系統平臺已通過BQB認證,具備高可靠性。

芯原BLE射頻 IP具備高性能射頻設計和低功耗優化,可以滿足高集成度、高性能、低功耗、低成本這四大優勢。在芯原BLE5.0 射頻測試報告中,所有參數均符合BT5.0協議規范。

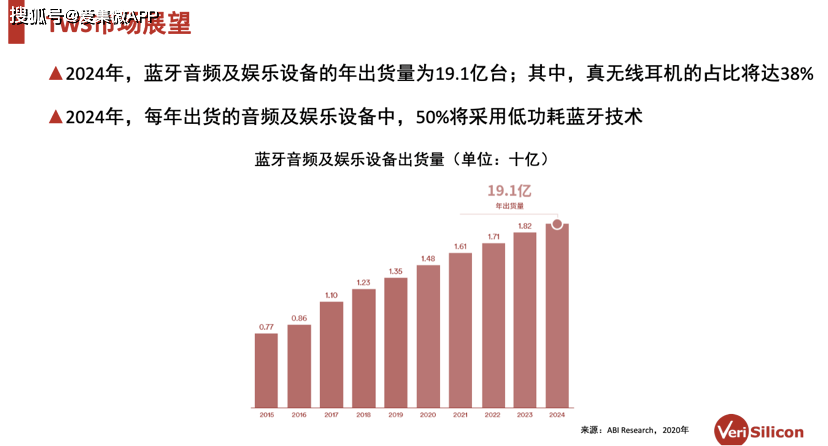

提到藍牙,不得不提其最大的應用市場耳機。從有線耳機到無線耳機,再到真無線耳機(TWS),其市場發展也是日新月異。據調研機構數據顯示,2024年,藍牙音頻及娛樂設備的年出貨量為19.1億臺,其中,真無線耳機的占比將達38%;2024年,每年出貨的音頻及娛樂設備中,50%將採用低功耗藍牙技術。

毫無疑問,TWS耳機占據著耳機市場中巨大的市場份額。汪洋認為,下一代 TWS 主晶片除了具備可靠連接、超低功耗、高音質的特點,還將具備主動降噪,AI輔助降噪,以及語音控制,智能控制的特點。

芯原GNSS射頻IP

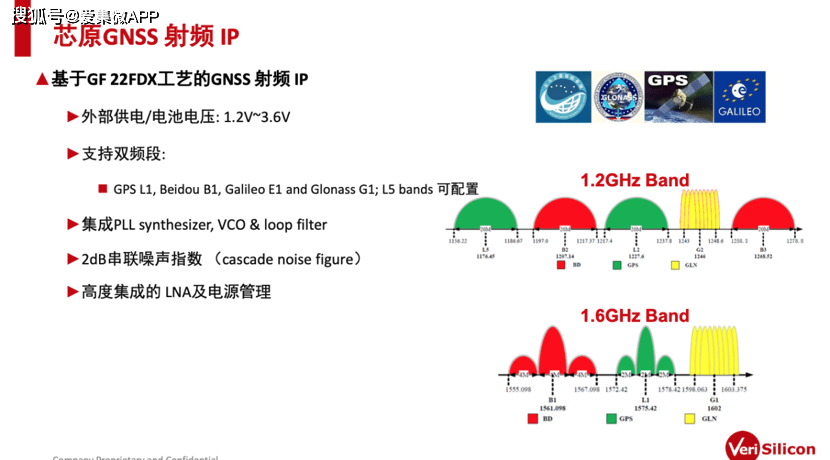

據汪洋介紹,基於GF 22FDX工藝的芯原 GNSS 射頻 IP,其外部供電/電池電壓為1.2V~3.6V,支持GPS L1、北鬥B1、伽利略E1 和格洛納斯 G1雙頻段,集成了PLL synthesizer, VCO & loop filter,同時擁有2dB串聯噪聲指數,以及高度集成的LNA及電源管理。

芯原GNSS 射頻測試晶片是獨立的射頻晶片以供 IP 驗證,其擁有完整的 Rx 通路,數字信號輸出至基帶處理,同時集成了集成 32K 振蕩器及 LDOs。芯原GNSS 射頻測試晶片可供 IP 評估,已經與基帶方案合作方一起通過集成測試,測試結果顯示 CN0 良好: ~40dB。

芯原的全球化布局

芯原成立於2001年,全球設有5個設計研發中心和10個銷售與客戶支持辦事處。目前在全球有900多位員工,其中80%的員工在上海和成都,80%的員工專職從事研發。2018年12月,芯原集團完成了拆紅籌重組,芯原上海已於2019年9月向上交所遞交科創板IPO申請,目前已成功過會。

汪洋表示,芯原擁有獨有的業務模式:晶片設計平臺即服務(SiPaaS)。SiPaaS 模式具體是指基於芯原自主半導體 IP 所搭建的技術平臺,為客戶提供一站式晶片定制服務和半導體 IP 授權的一種商業模式。正如20年前臺積電引領了晶片設計公司從「有制造」(IDM)到「無制造」(Fabless)的轉變,芯原致力於幫助晶片設計公司從「重設計」到「輕設計」的轉變。

堅持只做服務,不做產品,不與任何一家晶圓代工廠捆綁在一起,有著清晰定位的芯原正在正確的軌道上前進著。通過多年的自主研發及並購積累,芯原不僅可以提供世界一流的系統級晶片(SoC)和系統級封裝(SiP)一站式解決方案,同時針對消費電子、汽車電子、計算機及周邊、工業、數據處理、物聯網等領域建立起自己的IP護城河,成功發展成為一流的「IP Power House」。

根據 IPnest 統計,芯原2019年度半導體IP銷售收入在中國大陸排名第一、全球排名第七。芯原IP種類的齊備程度在全球半導體 IP 授權供應商中也具有較強競爭力。芯原至今已擁有高清視訊、高清音頻及語音、車載娛樂系統處理器、視訊監控、物聯網連接、數據中心等多種一站式晶片定制解決方案,以及自主可控的GPU IP、NPU IP、VPU IP、DSP IP 和ISP IP 五類處理器IP以及1,400多個數模混合 IP 和射頻 IP。

汪洋最後強調,未來擁有多樣化客戶基礎的芯原必將更好地應對日益增長的市場。

互動問答

Q:現在都在講AIoT,但是很多IoT設備需要能夠在路上,天空中,工廠內或海上平臺上運行。這些位置的共同點是通常對電子設備不太有利的環境。怎麼看物聯網數據傳輸這塊的環境困擾?

A:物聯網連接技術主要包括廣域物聯網和短距物聯網。其中功耗是核心的指標,不同場景下對於電源都有很高的要求,因此我們在設計物聯網連接技術時,也對半導體工藝技術進行了考量。隨著半導體工藝制程越往前演進,FD SOI工藝可以在不增加成本的同時,在功耗、性能和漏電功耗之間實現動態平衡,從而改善物聯網晶片的待機功耗和電壓功耗。

Q:BLE已經不少客戶在往28nm演進,隨著功耗要求越來越高,也有不少物聯網傳輸晶片往先進制程邁進,大家對於制程的關註和演進會不會形成類似很多消費電子晶片那樣的制程PK?

A:物聯網晶片除了對功耗有特殊的要求以外,成本也很重要。不同的物聯網連接技術對應不同的物聯網設備,終端設備的成本肯定是越低越好,所以主晶片的成本尤為重要。隨著半導體工藝制程不斷往前演進至14nm、7nm、5nm,性能會很好,但是有兩大挑戰,一是技術漏電,二是成本。我認為對於物聯網設備而言,對工藝節點的追趕沒有像手機那樣緊,需要綜合考慮功耗和成本。

Q:今天我們討論的是物聯網連接IP,最近「萬物智聯」的概念很火,在「智聯」方面,芯原可以為產業界提供些什麼樣的技術?

A:之前我講的都是連接性技術,即怎麼把數據從端傳到後臺,這是連接。連接帶來了數據以及對連接的智能處理,從而引申出一個概念「萬物智聯」。在智聯裡面,智慧怎麼體現呢?因此我們會加上AI技術,將實現本地化智能處理的芯原NPU技術集成到系統中。但是在通過AI技術實現智聯的形勢下,怎麼才能不顯著增加功耗和成本呢?這就需要做一些IP層面的集成,而芯原也一直在此領域布局。目前芯原大概有30多個AI客戶,50幾款晶片落地。

Q:芯原的IP營收目前中國排名第一,全球第七。芯原哪些IP是在業界具有領先優勢的?

A:芯原IP產品有上千種,除了物聯網連接技術IP,還有處理器IP。在一個完整的 SoC裡面,除了CPU以外,還需要圖像的處理、視訊的處理、編解碼、語音的處理、數據壓縮、顯示等等,這些模塊在數字處理流程中也是不可或缺的,因此芯原除了模擬和RF以外,在其他關鍵處理器IP上也做了很多的工作。無論是GPU、視訊轉碼方案、汽車中控、汽車儀表盤、桌面PC的顯卡、智能家居AI處理等等,芯原其實都有技術提供,而這些技術都是芯原經過十幾年的積累所得。

Q:ARM是目前低功耗藍牙SoC的主流架構,RISC-V目前也在蓬勃發展,芯原也是RISC-V的核心會員,怎麼看RISC-V的發展前景?芯原在這塊有一些自己的打算嗎?

A:RISC-V是一個很有發展前景的方向。在芯原的IP布局中可以看到,芯原沒有CPU IP,因此在CPU方面芯原會跟整個產業合作,不管是傳統CPU廠商,還是新興的RISC-V廠商,芯原都是採取開放的心態。RISC-V對於物聯網技術來說,也是很好的契合點,不光是商業模式,它的成本和功耗優勢對於物聯網設備供應商來說也是不錯的選擇,所以芯原會選擇與全球眾多的RISC-V廠商合作。

Q:物聯網,對於網路傳輸制式,速度,功耗,距離等各不相同,比較碎片化,這對我們這樣做IP的廠商而言會帶來哪些困難或者挑戰?

A:從IP角度來看,把連接技術做到極致就是挑戰,在物聯網連接技術上的每一個分支,不管是NB-IoT、藍牙還是LoRa,做到極致就必須使得數字電路設計夠小夠穩,同時也要追求可靠性和完整性,因此裡面的每一種模式包括晶片和IP都要打磨得很精致。芯原在做每一個RF 設計的時候,都要進行晶片的測試、迭代、調整,所以通過和FD SOI半導體工藝技術的結合,可以滿足物聯網連接技術所需的極致要求。

Q:從IP到晶片級解決方案,芯原可以再講一下服務內容以及特點嗎?

A:SiPaaS(Silicon Platform as a Service)模式具體是指基於芯原自主半導體 IP 所搭建的技術平臺,為客戶提供一站式晶片定制服務和半導體 IP 授權的一種商業模式。為包含移動互聯設備、數據中心、物聯網(IoT)、智能物聯網(AIoT)、汽車、工業和醫療電子在內的廣泛終端市場提供行業領先的、全面的系統級晶片(SoC)和系統級封裝(SiP)解決方案。芯原的機器學習和人工智慧技術已經全面布局智慧設備的未來發展。基於SiPaaS服務理念,芯原助力客戶在設計和研發階段領先一步,從而專註於差異化等核心競爭優勢。芯原的一站式端到端的解決方案則能夠在短時間內打造出從定義到測試封裝完成的半導體產品。

(校對/kaka)