尋夢新聞LINE@每日推播熱門推薦文章,趣聞不漏接❤️

據麥姆斯咨詢報導,先進封裝技術已進入大量移動應用市場,但亟需更高端的設備和更低成本的工藝制程。

更高密度的扇出型封裝正朝著具有更精細布線層的複雜結構發展,所有這些都需要更強大的光刻設備和其它製造設備。

最新的高密度扇出型封裝技術正在突破1µm線寬/間距(line/space)限制,這被認為是行業中的里程碑。擁有這些關鍵尺寸(critical dimension,CD),扇出型技術將提供更好的性能,但是要達到並突破1µm的壁壘,還面臨著製造和成本的挑戰。此外,目前還只有少數客戶需要這樣先進的封裝技術。

盡管如此,扇出型封裝在眾多市場上正變得越來越受歡迎。「移動設備仍然是低密度和高密度扇出型封裝的主要增長驅動力。」日月光(ASE)高級工程總監John Hunt表示,「隨著我們一級和二級的扇出技術獲得認證,汽車行業將開始加速發展。高端市場的服務器應用也在增長。」

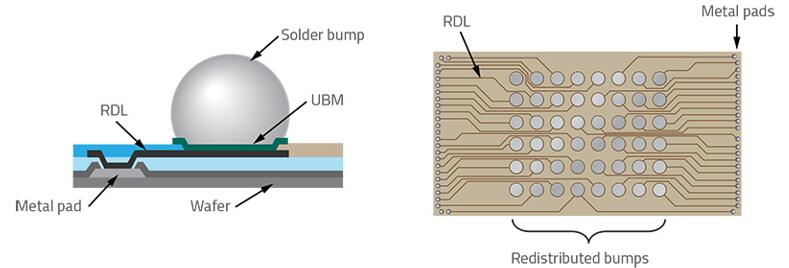

重布線層(Redistribution Layer,RDL)是扇出型封裝的關鍵部分。RDL是在晶圓表面沉積金屬層和介質層並形成相應的金屬布線圖形,來對晶片的I/O端口進行重新布局,將其布置到新的、節距占位可更為寬鬆的區域。RDL採用線寬(line)和間距(space)來度量,線寬和間距分別是指金屬布線的寬度和它們之間的距離。

圖1:重布線層

扇出型技術可分成兩類:低密度和高密度。低密度扇出型封裝由大於8μm的line/space(8-8μm)的RDL組成。高密度扇出型封裝有多層RDL,CD在8-8μm及以下,主要應用於服務器和智慧型手機。一般來說,5-5μm是主流的高密度技術,1-1μm及以下目前還在研發中。

「就設計規則的激進程度而言,目前仍然有各種各樣的扇出型技術。很多產品都受到外形尺寸、性能以及成本等因素的影響。」Veeco全球光刻應用副總裁Warren Flack說道,「具有較小CD的重布線層能夠減少扇出型封裝中的重布線層數。這能降低整體封裝成本並提高良率。」

成本是許多封裝廠需要考慮的因素。因為並非所有客戶都需要高密度扇出型封裝。挑戰性(非常小)CD的扇出技術相對昂貴,僅限於高端客戶。好消息是,除了高密度扇出型封裝之外,還有其它大量低成本的封裝技術可供選擇。

然後,另一方面,客戶也正在推動封裝廠商降低其製造成本,特別是對於扇出型封裝和其它先進封裝。在扇出型封裝中,有幾個工藝步驟,包括光刻——一種在結構上形成細微特徵圖案的方法。

在封裝領域,有幾種不同的光刻設備類型,例如對準式曝光機、直接成像、雷射燒蝕和步進式曝光機(stepper),每項技術能力不同。換言之,封裝廠商可能會使用不同的設備類型進行扇出型封裝。

什麼是扇出型封裝?

扇出型封裝技術在封裝市場是較為熱門的話題。在扇出型技術中,裸片直接在晶圓上封裝。由於扇出型技術並不需要中介層(interposer),因此比2.5D/3D封裝器件更廉價。

扇出型技術主要可以分作三種類型:晶片先裝/面朝下(chip-first/face-down)、晶片先裝/面朝上(chip-first/face-up)和晶片後裝(chip-last,有時候也被稱為RDL first)。

在chip-first/face-down工藝流程中,晶圓廠首先在晶圓上加工晶片,然後將晶圓移至封裝廠進行晶片切割。最後,通過晶片貼裝系統,再將晶片放置在臨時載板上。

EMC(epoxy mold compound,環氧模塑膠)被塑封在晶片和載板上,形成所謂的重構晶圓(reconstituted wafer)。然後,在圓形重構晶圓內形成RDL。

在RDL製造流程中,先在襯底上沉積一層銅種子層,再在該結構上塗布一層光刻膠,然後利用光刻設備將其圖案化。最後,電鍍系統將銅金屬化層沉積其中,形成最終的RDL。

RDL的CD取決於應用。許多扇出型封裝不需要先進RDL。在可預見的未來,5-5µm及以上的封裝仍將是主流技術。在高端領域,ASE正朝著1-1μm及以下的RDL進軍。與此同時,台積電(TSMC)也緊跟步伐,目前正在研發0.8μm和0.4μm的扇出型技術。先進扇出型技術終將支持高帶寬存儲器(high-bandwidth memory,HBM)的封裝。

「扇出型方法有很多種。我們可以看到CD越來越小,越來越有挑戰性。銅柱的間距也越來越小。」Veeco的光刻系統亞洲業務部門總經理Y.C. Wong說道,「通常,主流的RDL仍在5-5μm及以上。目前我們可以看到也有2-2μm或3-3μm在生產。而現在1-1μm還只是處於研發狀態。當5G真正發展起來以及隨著存儲器帶寬需求變高時,以上需求都將被驅動。這也將推動市場對2-2μm和3-3μm及以下的更多需求。」

盡管如此,所有扇出型技術仍然都面臨著挑戰。「扇出型封裝的主要挑戰是翹曲(warpage)/晶圓彎曲(wafer bow)問題。此外,晶片放置也會影響晶圓的平整度和晶片應力。所以晶片偏移(die shift)給光刻步驟和對準帶來了挑戰。」Yole分析師Amandine Pizzagalli說道。

成本也是關鍵因素之一。具有挑戰性CD的封裝往往更昂貴。相反,CD要求低的封裝則更便宜。在任何情況下,客戶對IC封裝的價格都是敏感的。他們希望盡可能降低封裝成本。因此,他們希望封裝廠商降低製造成本。

這個故事還有另外一面。封裝客戶可能想要一款具有挑戰性RDL的扇出型產品。但是該封裝技術必須達到一定的需求量才具有研發的可能性。如果封裝需求量達不到目標,則很難獲得回報。因此,目前來說可能還沒有動力驅動更小RDL的封裝研究。

對準曝光機(Aligners)vs. 步進式曝光機(steppers)

當然,光刻技術在扇出型和其它封裝類型中起著關鍵作用。在晶圓廠,光刻設備被用於奈米級的特徵圖案,這也是至關重要的。同時,在封裝廠,光刻和其它設備被用來處理凸點(bump)、銅柱(copper pillar)、RDL和矽通孔(TSV),這些結構都屬於微米級。

根據Yole的數據表明,2019年用於封裝的光刻設備市場規模預計將達到1.416億美元,高於2018年的1.287億美元。Pizzagalli稱,所有的新設備採購清單中,約85%涉及步進式曝光機,其次是掩模對準曝光機,占比相比前者低15%。

掩模對準曝光機和步進式曝光機都屬於光刻類別。為此,該工藝從光掩模版開始。設計人員設計IC或封裝,然後將其轉換成文件格式,再基於該格式開發光掩模版。

光掩模版根據給定圖形進行設計。掩模版顯影後,被運送到晶圓廠或封裝廠。將掩模版放置在光刻設備中。該設備發射光線透過掩模版,在器件上形成圖案。

多年來,掩模對準曝光機一直是封裝界的主流光刻設備。「掩模對準曝光機的工作原理是將掩膜版的全區域圖形投影到襯底上。由於投影光學器件沒有減少,掩模版必須放置在晶圓附近。因此,其分辨率被限制在約3μm line/space。」EV Group業務發展總監Thomas Uhrmann表示。

如今,掩模對準曝光機主要用於封裝、MEMS和LED(發光二極管)領域。「雖然在生產過程中很難達到3µm以下的line/space要求,但在先進封裝中,掩模對準曝光機還有其它優勢。例如,掩模對準曝光機在需要高強度和高曝光次數的凸點和厚抗蝕劑曝光領域具有性能和成本優勢。」Uhrmann說道。

然而,對於更先進的應用,封裝廠則會轉向使用一種稱為步進式曝光機的光刻系統。使用先進的投影光學系統,步進式曝光機的分辨率高於掩模對準曝光機。

步進式曝光機可以將圖像特徵以更小比例從掩模版轉移到晶圓上。不斷重復該過程,直到晶圓被加工完成。封裝領域步進式曝光機的主要參與者有Canon(佳能)、Rudolph(魯道夫)、Veeco(維易科)及其它競爭者。

對於許多應用來說,封裝廠商選擇使用步進式曝光機出於幾個原因。「當我們開始研究步進式曝光機可以做些什麼的時候,我們就可以提供一些顯著的改進。」Veeco公司的Flack說道,「縮小CD在過去幾年里一直是我們考慮的重要因素。步進式曝光機也正在縮小套刻精度以匹配CD。現在,它必須能夠處理更多不同尺寸的襯底。」

與此同時,在晶圓廠,晶片製造商使用193nm波長的光刻系統來進行特徵成像。然而在封裝廠,由於特徵尺寸更大,封裝廠無法使用此波長的設備。相反,他們使用的光刻機波長更長,如436nm(g-line)、405nm(h-line)和365nm(i-line)三種波長。

在封裝過程中,一些步進式曝光機僅具備i-line波長,而有一些則支持更多的波長。例如,Veeco推出的一種稱為寬波段步進式曝光機,就支持三種不同波長——436nm、405nm和365nm,通常是由寬波段光譜汞燈產生的。

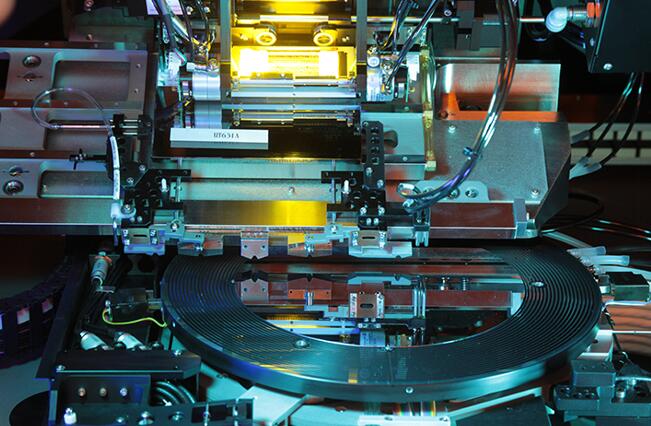

圖2:Veeco步進式曝光機內部構造

對於更具挑戰性的CD,該步進式曝光機可被調整為支持「僅i-line」模式,用於處理1-1μm的特徵圖形。此外,該設備還支持「ghi」模式,處理2-2μm及以上的應用。

步進式曝光機可用於一系列IC封裝中,包括扇出型封裝。在扇出型封裝中,光刻設備有助於完成RDL。

這些系統還必須處理晶片偏移問題。如上文所述,當晶片嵌入重構晶圓中時,它們會隨著制程發生移動,造成晶片偏移,從而影響良率。

為了解決這個問題,業界正在開發具有更好對準技術的光刻設備,以補償晶片偏移。「有兩種方法可以解決這個問題。從光刻的角度來看,你可以盡可能多地修正它、可以調整晶圓上的刻度、可以調整放大率等。但這是假設所有晶片都以同樣的方式移動的情況下。如果偏移是隨機的,那麼幾乎不可能糾正這種情況。」Veeco的Flack說,「對於高端應用,我們需要努力確保晶片不會偏移。在某些情況下,可以通過放置和對準晶片的技術來做到。」

晶片偏移仍然是所有扇出技術持續存在的挑戰。另一挑戰是制備RDL。在5-5μm範圍內通過RDL進行扇出封裝幾乎沒有或完全沒有問題。甚至在2-2μm範圍內的RDL也在生產中。

隨著扇出型封裝不斷向1-1μm及以下發展,挑戰越來越大。目前能解決此問題的訣竅是以高良率制備更精細的RDL。

目前該行業已經可以達到1-1μm的分辨率。例如,Veeco在步進式曝光機中使用「僅i-line」模式,顯示分辨率為1-1μm。步進式曝光機具有可變數值孔徑(numerical aperture,NA)物鏡和1X掩模板。

然而盡管如此,還是存在一些挑戰。根據Veeco和Imec最新的論文中所述,在制備RDL過程中,必須保證銅足夠厚,以降低金屬線的電阻。因此,光刻膠的縱橫比必須最大化。根據該論文,這需要具有較大焦深的光刻設備來處理扇出技術出現的高度變化。

同時,有些公司提供「僅i-line」系統。例如,佳能最新的i-line設備採用孔徑為0.24的物鏡,確保分辨率≤0.8μm。

「領先的1µm先進封裝工藝需要使用化學放大原理的光刻膠,由於其光致酸產生劑的特性,僅對i-line波長敏感。因此,它需要i-line曝光光源來做到小於1µm的分辨率。」佳能的行銷經理Doug Shelton說道,「要求寬波段曝光的客戶將使用成熟的DNQ光刻膠來對準粗糙的圖案層,這些光刻膠對i-line和h-line波長敏感,而對g-line波長不敏感。對於那些挑戰性較小的應用,我們可以利用系統,該系統可以選擇允許寬波段i/h-line曝光,以提高粗加工的產出量。」

因此,使用當今的技術將RDL突破1µm是有可能的,但目前尚不確定。這也是封裝行業一直在爭論的話題。然而,不管步進式曝光機的波長類型,突破1-1μm都存在一些挑戰。光刻設備當然是有能力達到的,但目前的RDL流程還存在其它問題。

「當降到1-1μm以下時,會遇到其它與光刻無關的問題,這將限制其被採用的速度。」Veeco公司的Flack說道,「只要種子層占銅線寬度的一小部分,它就能很好地工作。當小於1μm時,種子層占線寬的比例增加,就會出現低良問題。」

簡而言之,傳統的RDL工藝是突破1-1μm的潛在障礙。「在這一點上的轉變,將是行業面臨的真正挑戰。」Flack表示。

因此,該行業同時也在研究其它工藝流程,如雙大馬士革工藝(dual damascene)。多年來,晶片製造商一直使用雙大馬士革工藝來做到晶圓廠後道工藝(backend-of-the-line,BEOL)中晶片的銅互連。

在雙大馬士革工藝中,BEOL和封裝的工藝步驟類似。在封裝中,絕緣層沉積在襯底上。然後,對溝槽進行圖案化和刻蝕,並用銅填充溝槽。

對於封裝來說,雙大馬士革工藝是可行的,可以將RDL降到1-1μm及以下。「這項工藝很好,但價格昂貴。有技術解決方案,但成本效益可能不高。」Flack說。

台積電(TSMC)目前也在探索雙大馬士革工藝,但對大多數廠商來說,價格太昂貴了。因此,該行業還需在此「競技場」上做到經濟效益的突破。

雷射成像、燒蝕等光刻技術

雷射直接成像(laser direct imaging)是另一種用於封裝的光刻技術。雷射成像類似於直寫或無掩模(maskless)光刻。它不需要直接使用掩模版就能做到在晶片上進行加工,因此削減了封裝成本。

奧寶科技(Orbotech)和迪恩士(Screen)是雷射直接成像系統的供應商。據消息稱,另一家公司Deca也開發了具有專利的雷射直寫技術。

雷射成像可以解決扇出型封裝中的晶片偏移問題。如上所述,第一步是構建重構晶圓。然後,使用晶片貼裝系統將晶片放置在晶圓上。

「問題就出現在這里。當你把晶片放在上面時,晶片彼此之間並不完美。很難將晶片精確地保持在我們想要的微米範圍內。」Deca首席技術官Tim Olson表示。

Deca公司的「自適應圖案化(Adaptive Patterning)」技術則是解決晶片偏移的一種方法。ASE是Deca的投資者,正在基於這種圖案化技術生產M系列扇出型產品。

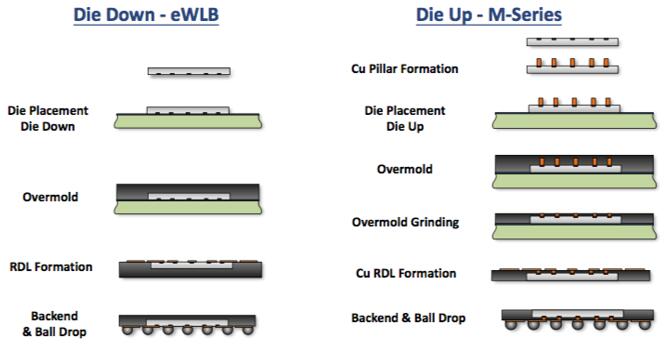

圖3:M系列扇出型封裝與傳統eWLB扇出型封裝的對比

Deca的技術包括四個模塊的工藝流程——晶圓準備、拼板、扇出和檢查。它支持研發具有更精細的RDL的5-5μm多層扇出型封裝。

在晶圓準備過程中,可在晶片上電鍍銅。然後,在拼板步驟中,使用高速系統以每小時28000顆晶片的速度將晶片放置在重構晶圓中。相比之下,傳統的晶片貼裝系統每小時只能完成2000多顆晶片。

然後,通過使用檢查技術來測量晶圓上每個晶片的實際位置。Olson解釋道:「晶片測量檢查是拼板加工過程中的最後一步,用於製造過程中每個拼板的實時設計。」

然後,RDL以晶片先裝/面朝下的流程開發。在曝光步驟期間,系統重新計算RDL圖案以適應每片晶圓中的每顆晶片偏移。這個過程只需要28秒。總產出量為每小時120片晶圓。

「自適應圖案化是一種系統,旨在自動補償製造過程中的自然變量,而不是專注於消除所有變量。」Olson說道,「在典型的應用中,通過晶片貼裝、註塑和其它工藝步驟,允許晶片在‘X’軸和‘Y’軸上的變量高達60μm。自適應圖案化通過製造中的實時設計自動消除了97%的變量,做到了2μm以下的有效互連公差。目前我們正在開發中的下一代自適應圖案化技術將支持2μm的特性,尺寸將縮小為0.8μm。」

ASE計劃在2019年或2020年使用來自Deca的相同技術,提升面板級扇出型封裝。同時,該封裝也將使用自適應圖案化技術。

與此同時,Suss MicroTec公司也在開發一種叫做雷射燒蝕(laser ablation)的幹法圖案化工藝。Suss的準分子燒蝕步進式曝光機結合了基於掩模版的圖案化燒蝕。可以做到3μm的line/space,而2-2μm也在進展中。

「準分子雷射燒蝕是利用高功率紫外(UV)準分子雷射源的特性直接去除材料。典型的波長是308nm、248nm和193nm。」Suss光子系統總裁兼總經理Markus Arendt說道,「準分子燒蝕瞬間將相容的目標材料(即聚合物、有機電介質)從固態轉化為氣態和副產物(即亞微米幹碳顆粒),從而產生很少甚至沒有熱影響區以及更少的碎片。」

通過使用該技術,Suss一直專注於晶圓級工藝。此外,他還研發了雙大馬士革工藝RDL流程及其它技術。

「我們的產品路線圖包括許多新項目。」Arendt說,「然而,最值得注意的兩個問題是:(1)新的大視場、高NA投影物鏡,可在生產中做到2μm的line/space;(2)雙雷射版本,可做到更大的掃描光束,從而顯著提高產出量並降低購入成本。」

並且,Brewer Science公司正在研究另一種方法。它在註塑混合物中使用一種薄膜,就像模板一樣工作,可解決晶片偏移問題。「這是環氧塑封材料的替代品。」Brewer高級技術執行總監Rama Puligadda說道,「你預先形成模板,然後可在那里用矽製造空腔。」

顯然,用於封裝的創新光刻解決方案並不缺乏。但是要突破1-1μm還需要繼續努力。即使業內人士都知道這一點,但也必須滿足客戶苛刻的成本要求。這些因素都會讓這個行業忙碌一段時間。

推薦培訓:

《MEMS製造和封測培訓課程》將於3月29日至31日在無錫舉行,本課程邀請MEMS業內優秀講師,重點剖析MEMS產業鏈的重要環節:(1)MEMS製造工藝;(2)典型MEMS器件工藝流程(如MEMS麥克風、壓力傳感器、非制冷紅外探測器、MEMS微鏡、噴墨列印頭等);(3)MEMS封裝技術;(4)MEMS測試技術(如加速度計、陀螺儀、磁傳感器、壓力傳感器、MEMS麥克風等);(5)關鍵工藝設備和材料等,為大家展現MEMS產業的全貌和重要知識點。如果您有興趣,請聯繫:

麥姆斯咨詢

聯繫人:郭蕾

E-mail:Guolei#memsconsulting.com(#換成@)

課程簡介:http://www.mems.me/mems/conference_201901/7578.html