尋夢新聞LINE@每日推播熱門推薦文章,趣聞不漏接

DPDK在專注數據面報文處理的同時,一直緊跟著網路發展的脈搏以開放的姿態融合不斷湧現的各種新的網路設備。從最初的普通網卡,到集成虛擬化和交換功能的高級網卡,再到各種網路SoC(片上系統)設備,到現在最熱的基於FPGA的Smart NIC,DPDK一直走在軟件定義網路技術發展的最前沿。近年來,數據中心異構化的趨勢出現,基於雲的數據中心如何使用加速器來進行存儲,網路以及人工智能的加速,能為炙手可熱的話題,在剛結束的APNET’18,華為與騰訊都分享了技術方向與實踐演進過程,基於Linux Foundation的開源項目,對這種架構的支持,在軟件的持續性與高質量保證上至關重要。

本文首先分析FPGA在網路加速中的優勢,闡述了FPGA部署的軟件基礎架構的支撐,然後介紹了英特爾FPGA加速開發棧,最後詳細說明DPDK 18.05版本中發布新特性,這是第一款支持FPGA加速的通用網路軟件框架。

FPGA為網路業務提供卓越的性能加速

毋庸置疑,FPGA(Field Programmable Gate Array)早已是數據中心計算和網路加速的寵兒,靈活地通過軟件更改、配置器件內部連接結構和邏輯單元,完成既定設計功能的數字集成電路晶片不僅可以達到近似ASIC的性能,而且可在不到一秒的時間進行再編程。其數據路徑可精確匹配、靈活多變的適應用戶工作負載,並提升數據中心的性能、功效和利用率。長期看,還可以有效降低數據中心的總體運維成本, 減少基於專用ASIC加速的重復投資。微軟是這方面的先行者,微軟發表了大量論文與學界、工業界分享進展,探討挑戰。

FPGA在網路加速中的優勢概括起來有三點:靈活性、並行性和低延遲。相對於研發成本高,研發周期長的ASIC,可配置的FPGA無疑是非常靈活的。不同於馮·諾依曼結構,FPGA 同時擁有流水線並行和數據並行,例如處理一個網路包,一般要經過解析、分類、查表和修改這幾個基本步驟,複雜的網路包還需要流量管理、限速和報文復制等功能。FPGA可以通過搭建針對每一級處理的流水線,做到報文處理指令和報文數據的並行進而加速網路。低延遲得益於FPGA的精確可控報文處理步驟,在實時性要求高的領域比如金融,有著非常大的市場。

不過FPGA也不是萬能的,相比於軟件開發,FPGA的開發周期要長很多,一個FPGA版本的開發需要經過編譯、分析綜合、布局布線和時序分析等多個步驟,這些步驟一般都是以小時為單位計算。至於調試,也沒有GDB的單步調試方便,FPGA的在線調試全靠晶片內置的邏輯分析儀抓波形,通過分析「天書」一樣的波形圖來解決。另外,受限於片內的資源,FPGA在實踐中主要聚焦在網路底層的報文處理。

就FPGA的開發而言,從功能上可以分為可固化的接口部分和靈活多變的用戶業務邏輯部分,接口部分的開發如PCIe、DDR、以太網MAC和PHY與硬件緊密相連,且一旦單板做好改動較少,而用戶業務邏輯會隨著新功能的加入而不斷演進和變化,這才是體現FPGA的靈活性的地方。

從上面的分析我們可以看到,FPGA的部署和應用需要一些基礎架構層面的支撐,這些支撐有軟件方面的,也有FPGA方面的。軟件方面又分為公共軟件架構部分和FPGA晶片特定的軟件部分。在接下來的章節中,我們將對此做詳細的描述。

英特爾FPGA加速開發棧

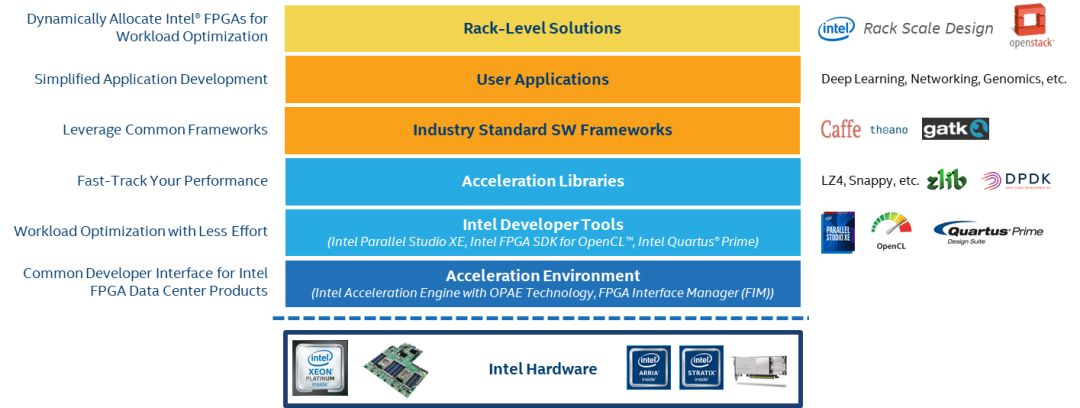

這里關注FPGA和晶片特定軟件的基礎架構支撐部分,圖1描述了系統架構與開發層次,開發者可以依據項目需要,安排軟件開發人員在適合的層次上輕鬆地利用英特爾FPGA。Intel發布了OPAE軟件, 提供可從虛擬機和容器調用的線程安全應用編程接口 (API),能高效隔離軟件與FPGA開發者的相互依賴。利用基於DPDK的軟件接口API,可以無縫支持當前與後續的FPGA設備,有效保證了軟件的移植性與獨立性。RTL開發者也能清晰依賴軟件接口來進行基於模塊的獨立開發。

圖1英特爾FPGA加速堆棧

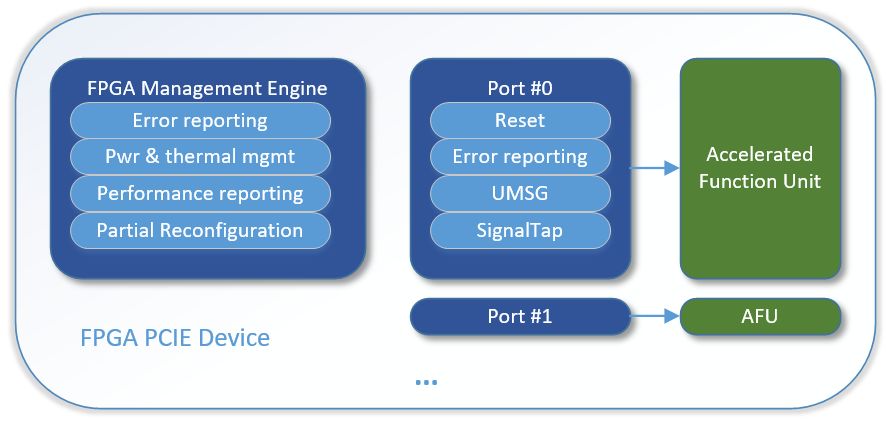

從應用模式上來看,如圖2所示,整個FPGA分為固化的藍色部分(FPGA Interface Manager),和靈活可變的綠色部分(Accelerated Function Unit)。藍色部分主要包含FPGA外圍接口和FPGA配置管理,綠色部分代表的是用戶自定義邏輯,一片FPGA可以根據資源大小提供一個或多個AFU(加速功能處理單元)。這種應用模式可為設計工程師帶來諸多優勢:

- 節省開發人員的時間,使其專注於提高解決方案的價值

- 支持跨多個英特爾 FPGA 外形產品重用代碼

- 構建全球首個用於英特爾 FPGA 數據中心產品的常見開發人員界面

- 靈活的FPGA池化和資源共享成為可能

圖2 FPGA Interface Manager

開放可編程加速引擎 (OPAE) 技術是一個軟件編程層,它提供了一個適用於各代 FPGA 產品和平台的 API。它旨在最大限度降低軟件開銷和延遲,同時為硬件特定的 FPGA 資源詳細信息提供一個抽象層。為了培養開放的生態系統並鼓勵使用 FPGA 加速功能處理數據中心工作負載,英特爾向行業和開發人員社區開放了這一技術。

- 輕量級的用戶空間庫 (libfpga)

- 許可:FPGA API (BSD)、FPGA 驅動程序 (GPLv2)

- FPGA 驅動程序向上遊移動到 Linux* 內核

- 支持容器,虛擬機和裸機平台

- 包括指南、命令行實用程序和示例代碼

DPDK的FPGA加速框架

針對FPGA的網路加速應用,DPDK 18.05版本正式發布了第一款支持FPGA加速的通用軟件框架。這套框架解決了FPGA應用時遇到的3個最重要需求:

- 在DPDK里支持FPGA管理的設備類型

- 如何將DPDK的高性能驅動與AFU(加速功能單元)關聯

- FPGA加速設備的引入要能最大限度的兼容開源API,比如DPDK API

對於FPGA的管理,DPDK 18.02的發布版本中新提供的rawdev類型結構,可以提供很好的適配。rawdev的優勢主要體現在兩點:業務無關性和豐富的操作接口。FPGA作為一種靈活可配置的晶片,它可以通過下載不同的Bitstream實例化不同類型的加速設備如網路加速設備和加解密加速設備,因此FPGA管理必須由一種業務不感知的類型結構來操作,rawdev正好切合了這一點。此外,在rawdev內部提供了大量的操作接口如固件下載、屬性獲得、設備管理等可以用來作為FPGA的管理接口。

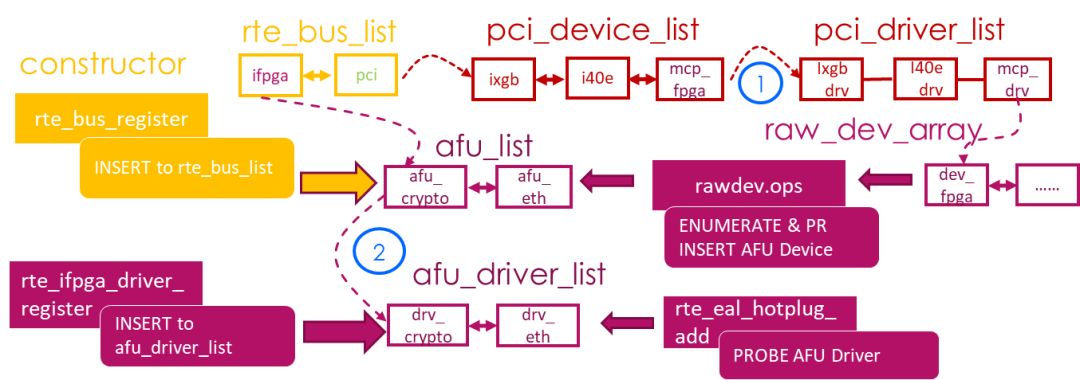

對於DPDK驅動與AFU的關聯,我們提出了FPGA-BUS這一新的通用總線。在FPGA基礎架構層面的支撐下,FPGA作為一個PCIe設備不再與業務關聯,取而代之的是FPGA內部的AFU與用戶驅動的綁定。在做到時,我們的出發點是盡量的復用現有DPDK PCI BUS Scan流程,最好不修改。事實上,通過引入FPGA-BUS,我們有效地做到了這一點。用戶只需要編寫基於AFU的軟件驅動而不是PCI驅動,每個AFU都有自己的設備ID,AFU驅動通過AFU ID與AFU設備關聯。如圖3所示,引入FPGA-BUS後,整個驅動的加載以兩次掃描的形式清晰的呈現給用戶:PCI BUS 掃描和 FPGA BUS 掃描。

- PCI BUS 掃描: FPGA 作為一個PCIe設備被掃描並加載其rte_rawdev驅動,這是標準的DPDK PCI BUS 掃描

- FPGA BUS 掃描: rawdev根據用戶配置載入不同的AFU並Hot Plug觸發FPGA BUS 的掃描,從而加載AFU 驅動

圖3 兩次BUS 掃描和AFU驅動加載

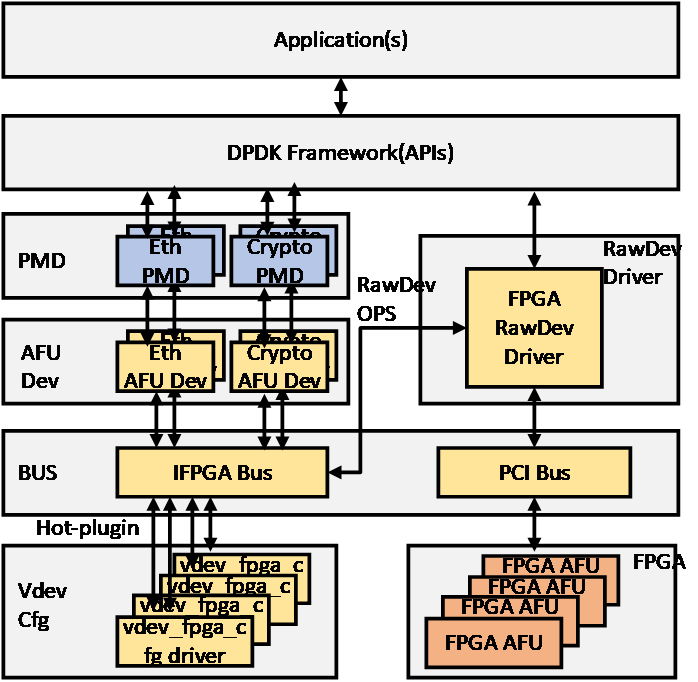

圖4 DPDK FPGA加速框架示意圖

整個加速框架的詳細架構如圖4所示,我們引入vdev來進行AFU配置參數的載入,FPGA與其rawdev關聯,AFU驅動與AFU設備關聯。由於rawdev屏蔽了硬件細節和FPGA BUS的引入,DPDK 應用感知不到它所調用的是FPGA加速設備還是普通的NIC加速設備。

英特爾FPGA加速堆棧與DPDK FPGA加速框架的集成

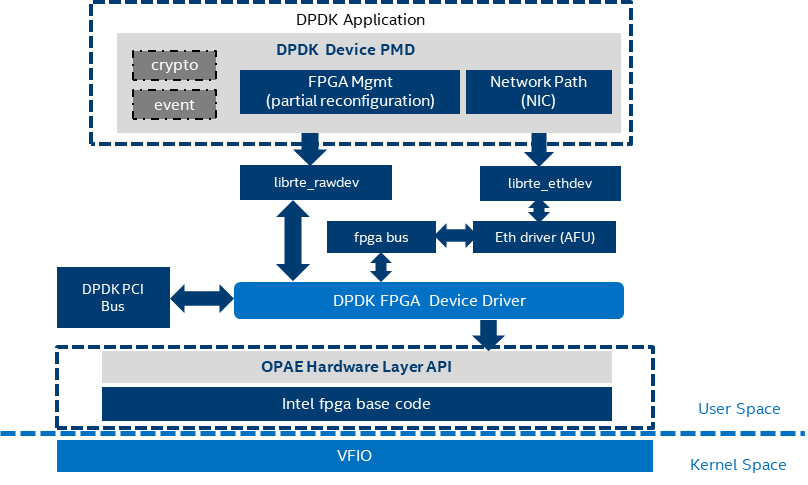

圖5 英特爾FPGA加速堆棧與DPDK FPGA加速框架的集成

如圖5所示,英特爾FPGA加速堆棧的軟件部分OPAE以Base Code的形式提供給DPDK,DPDK 的rawdev結構通過OPAE管理和配置FPGA,FPGA-BUS提供對AFU的管理和驅動加載。基於這套架構,DPDK提供了軟件框架可以更輕鬆地開發和部署英特爾FPGA設備,優化數據中心的工作負載。在報文處理領域,如果把DPDK比作「倚天劍」的話,那麼FPGA就是「屠龍刀」,這兩者強強聯手威力無窮,持有這兩個武器的開發者,在數據中心網路加速中可以說是無人能敵。

文章轉載自DPDK與SPDK開源社區公眾號,作者二維碼如下:

www.ssdfans.com